Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

2024-04-01

En la actualidad, los servomotores en las máquinas herramienta de CNC domésticas generalmente están equipados con codificadores incrementales, mientras que la precisión de los codificadores incrementales no es demasiado alta y la salida es señales paralelas. Para mejorar su precisión, es necesario aumentar el diseño del codificador. Dificultad y aumento de la salida de señales paralelas, que no conducen a la comunicación a larga distancia entre la Unidad del servo y el codificador. Se usa el codificador absoluto, excepto que su precisión es varias veces mayor que la del codificador incremental. La comunicación en serie de alta velocidad guarda líneas de comunicación para la comunicación a larga distancia. En el otro extremo del codificador, el codificador CPLD y el codificador absoluto se utilizan para la comunicación en serie de alta velocidad. El CPLD luego convierte la información del codificador recibido en transmisión de datos paralelos. El DSP en la unidad de servo realiza control aritmético. Este documento proporcionará el diseño de software y hardware de la comunicación en serie de alta velocidad entre CPLD y el codificador absoluto .

diseño de hardware

El hardware se compone principalmente de tres módulos: fuente de alimentación, CPLD y sus circuitos periféricos y circuito de interfaz de codificador absoluto.

Módulo de poder

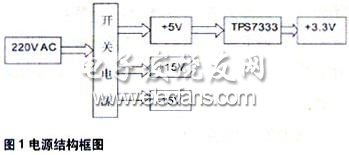

El módulo de alimentación consiste en un circuito de fuente de alimentación de conmutación y un chip de fuente de alimentación DC/CC, como se muestra en la Figura 1.

La fuente de alimentación de conmutación en la figura convierte el voltaje de la cuadrícula de CA de 220 V en +5V, +15V, -15V. La fuente de alimentación de conmutación puede filtrar varias interferencias en la cuadrícula de alimentación, y el transformador en la fuente de alimentación de conmutación será de 220 V AC y la salida es de + 5V, + 15V, -15V está aislado, el circuito interno también usa TL431 para ajustar el ajuste del El ancho del pulso de conducción del tubo de interruptor, por lo que la regulación anti-interferencia, seguridad, estabilidad y voltaje de la fuente de alimentación de conmutación es mejor. El TPS7333 es un chip DC/DC. El voltaje de CC de +5V se convierte en un voltaje de CC estable de +3.3V para usar por el CPLD. El TPS7333 tiene una mejor eficiencia de conversión, confiabilidad y regulación de voltaje. Se puede usar en el rango de voltaje de +3.77V- +10V. La conversión +3.3V hace que el CPLD se queme debido a que el voltaje de entrada es demasiado alto.

CPLD y sus módulos de circuito periférico

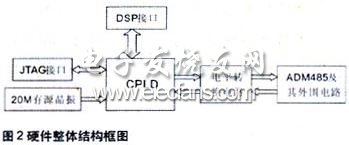

El CPLD y sus módulos de circuito periférico están compuestos principalmente de CPLD, circuito de interfaz de descarga de programación CPLD (interfaz JTAG), circuito de interfaz DSP, oscilador de cristal activo, circuito de conversión de nivel y ADM485 y sus circuitos periféricos (circuito de interfaz responsable de la comunicación con el encoder) . Figura 2).

Este CPLD de diseño utiliza EPM570T144C5 de Altera, que pertenece al Max II de Altera. Max II es menor en costo que Max I y consume menos energía. El dispositivo tiene más celdas macro y el retraso del dispositivo se controla dentro de los 6 ns. Con un rendimiento de alto costo, el EPM570T144C5 tiene 570 macrocellos. El número de pines en el chip es 144, de los cuales 116 están disponibles en puertos de E/S, por lo que los recursos de este chip son suficientes. El CPLD es el principal responsable de la comunicación en serie de alta velocidad con el codificador absoluto, y está controlado por el comando DSP para reenviar los datos del codificador y otra información al DSP en paralelo.

La interfaz JTAG se usa principalmente para descargar el archivo ejecutable al CPLD, instalar el entorno de desarrollo de la compañía Altera - Quartus II en la PC y compilar el programa VHDL escrito en este entorno de desarrollo para garantizar que la compilación no esté libre de errores y se implementa la función. Conecte el cable de descarga a la interfaz JTAG y descargue la placa CPLD a través de la herramienta de descarga de programación proporcionada por Quartus II.

La interfaz DSP consta de 8 líneas de datos, 3 líneas de dirección y 1 línea de control. Las 8 líneas de datos son responsables de transferir los datos del codificador y otra información. Las 3 líneas de dirección son responsables de transmitir comandos DSP y decodificar en el terminal CPLD. El CPLD transmite los datos del codificador u otra información al DSP a través de 8 líneas de datos de acuerdo con el comando decodificado. La línea de control completa principalmente el control sincrónico del CPLD y el DSP.

El oscilador de cristal activo de 20 m proporciona principalmente un reloj de referencia para el CPLD. Bajo la señal de conducción de la señal del reloj, el CPLD genera una velocidad de baudios de 2.5 MB/s para comunicarse con el codificador, y genera un reloj de 10M Hz para algunas señales de control lógico. Proporcionar una frecuencia de reloj de 20M Hz requiere un voltaje de CC de 3.3V desde la fuente de alimentación.

El circuito de cambio de nivel es el principal responsable de convertir 3.3V a 5V o 5V a 3.3V, porque el núcleo y los puertos de E/S del CPLD requieren un voltaje de suministro de 3.3V, que se requiere para codificadores ADM485 y absolutos. Tanto el voltaje de suministro como el circuito del controlador de puerto de E/S son de 5V, por lo que es necesario convertir 3.3V a 5V o 5V a 3.3V con el chip de conversión de nivel LVC4245A.

ADM485 y sus circuitos periféricos son la conexión de hardware entre CPLD y la comunicación de alta velocidad del codificador absoluto. El voltaje de trabajo de ADM485 es de 5V, y su velocidad de comunicación máxima es de 5 MB/s. El uso de dos chips ADM485 para la comunicación de acoplamiento puede mejorar la capacidad anti-interferencia en la línea de comunicación, y la distancia de transmisión más larga puede alcanzar 1.2 km. El circuito periférico se muestra en la Figura 3. La mitad derecha de la línea punteada pertenece al circuito periférico del codificador absoluto. Las resistencias de pull-up y desplegable son de 1k ohmios, la resistencia limitante de corriente es de 220 ohmios y el SDAT ADM485 es el pin de salida de datos. ADM485 es SRQ es el pin de entrada de datos, DE de ADM485 es el pin de control externo, este pin está controlado por CPLD. Dado que el protocolo de comunicación RS-485 es medio dúplex, ADM485 solo puede estar en el estado de enviar datos o recibir datos. Cuando ADM485 es de alto, ADM485 está en estado de salida de datos (es decir, CPLD recibe datos). Cuando DE de ADM485 es de bajo nivel, ADM485 está en el estado de entrada de datos (es decir, CPLD envía datos).

Compartir:

Realizar consulta

Ms. carol Dong

Número de Teléfono:86-431-85543703

Fax:86-431---88634119

Móvil:+8613894866263

Email:sales@encoders.com.cn

Dirección:333Feiyue Donglu, Changchun City, Jilin Province. China, Changchun, Jilin

Sitio movil

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.