Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

2024-03-18

Resumen: Para resolver algunos problemas en el sistema de monitoreo de definición estándar, se diseña un sistema de compresión de video de alta definición basado en TMS320DM365. Algoritmo de compresión de video ITU-T H. 264 (compresor de hardware integrado DM365), la señal de video analógico de alta definición se convierte en una señal de video digital mediante un chip de videos dedicado TVP7002, compresión de datos en DM365, los datos del brazo embarcado se empaquetan y se transmiten al Internet, a través de la decodificación del software de PC para la reproducción de video. La práctica ha demostrado que este esquema de codificación ha completado el pozo de compresión y transmisión de datos y cumple con los requisitos de diseño.

Palabras clave: compresión de video; DM365; H. 264; transmisión de red

En las aplicaciones de videovigilancia, la videovigilancia tradicional tiene una alta claridad de imagen (resolución CIF a D1), dificultad para administrar y mantener muchos cables, configuración complicada de muchos dispositivos y expansión inconveniente. Estos factores restringen seriamente la efectividad de la gestión de la seguridad. Mejora, pero también brinda una oportunidad para el desarrollo de videovigilancia de alta definición, este documento analiza el diseño de hardware del codificador de video HD basado en DM365.

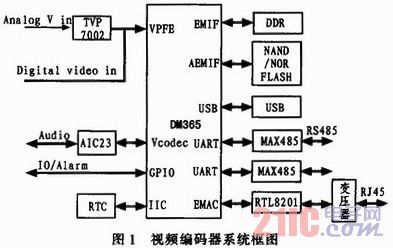

1 Plataforma de hardware Diseño general TMS320DM365 Continúa la arquitectura del procesador DM355 de la familia davincitm, que integran un núcleo ARM926EJ-S, un subsistema de procesamiento de imágenes (VPSS), un coprocesador de codificadores H. 264 HD HDVICP y un MPEG-4/JPEG HD COPRODER MJCP MJCP MJCP HDVICP y un MPEG-4/JPEG HD COPRODer MJCP MJCP MJCP MJCP , Soporte de códecs multiformato H. 264, MPEG-4, MPEG-2, MJPEG y VC1 para una alta flexibilidad de video. DM365 puede emitir simultáneamente 720p, D1, CIF Three Streams, o más combinaciones, y la velocidad de codificación es ajustable y admite Hardware OSD. El procesador tiene una interfaz periférica rica, y el usuario puede conectar convenientemente el subsistema. Este documento adopta TMS320DM365 como CPU principal, recopila los datos de video de entrada y realiza el procesamiento de transmisión de red de compresión correspondiente, y diseña un codificador de video digital basado en la arquitectura DM365. Además de DM365, el sistema también tiene un convertidor A/D de video A/D de alta definición, códec de audio, almacenamiento, ethernet, puerto serie y otros módulos. El sistema se ejecuta en el sistema operativo Linux y tiene las características del buen rendimiento en tiempo real, la velocidad de comunicación rápida, la alta calidad de imagen, el rendimiento estable, el bajo precio y el antivirus.

El diagrama de bloque general del sistema se muestra en la Figura 1. El sistema usa DM365 como CPU principal, módulo de audio externo DM365, módulo de entrada de video, módulo de almacenamiento, puerto serie y módulo de transmisión de red. La plataforma consta de dos partes: la parte de entrada de video y procesamiento de imágenes y la parte de salida de video.

Este artículo se refiere a la dirección: http: //

Entrada de video y parte de procesamiento de imágenes: señal de video analógica de alta definición de entrada TVP7002, después de la codificación A/D, se convierte en una señal de video digital de alta definición, y esta señal digital se emite a DM365. Este módulo DM365 realiza principalmente compresión H. 264 y puede lograr el filtrado de ruido, la estabilización de video, la detección de la cara, el balance de blancos automáticos, el enfoque automático, la exposición automática y la mejora del borde. Además, también inicializa todos los dispositivos I2C en el sistema para implementar el intercomunicador de audio y voz.

PARTE DE SALIDA DE VIDEO: Microprocesador de brazo integrado DM365, la función central de este procesador es reenviar la secuencia de datos, el módulo de memoria externo, el módulo Ethernet, el módulo de puerto serie, etc. El brazo primero completa el RTP, UDP y la encapsulación IP de los datos comprimidos, y luego pasa a través del marco MAC y finalmente completa la transmisión del paquete de datos a través del controlador Ethernet PHY. Además, ARM también es responsable de analizar los datos recibidos, reenviar los comandos de parámetros relevantes enviados por la PC, realizar la configuración de operación correspondiente (velocidad de compresión de video, velocidad de cuadro, etc.) e implementar el control periférico a través del puerto serie (controlador PTZ , lente) etc.), el procesamiento de la entrada y salida de alarma a través de GPIO, y así sucesivamente.

2 diseño de módulos

2.1 Módulo de entrada de audio de video Hay una interfaz VPFE en el DM365, que puede admitir formatos de entrada de video en múltiples formatos. El sistema realiza la entrada de video HD de 1 canal, y el chip de conversión HD A/D adopta TVP7002. El TVP7002 puede realizar señales digitales de R/PR, C/Y, B/Pb con una tasa de conversión de hasta 165 MHz. Se utiliza en muchos entornos de video digitales de alta definición con una resolución de hasta 1080p. El DM365 está configurado a través del bus IIC. Los registros internos TVP7002 están configurados correctamente para procesar fuentes de video de resolución 720p. Los datos de video A/D se emiten desde el puerto de video digital TVP7002 al DM365 VPFE. El sistema también proporciona una interfaz de entrada de video digital de alta definición, el coprocesador HDVICP puede proporcionar H en 1 formato de 1 280x720p30. La codificación o decodificación de video estándar 264, y el coprocesador MJCP, además del estándar JPEG, también puede proporcionar codificación o decodificación de video MPEG-4 en el formato 1 920x1 080p24.

El sistema se da cuenta de que una salida de línea y estéreo a través de AIC23, DM365 se configura a través del bus IIC y AIC23 está conectado al puerto MCBSP de DM365. El MCBSP del DM365 se utiliza como un canal de datos bidireccional a través del cual se transmiten todos los flujos de datos de audio y admite diferentes formatos de datos.

2.2 Módulo Ethernet El sistema incluye una interfaz de red I-Channel 10/100m, el DM365 tiene un controlador MAC y un chip Ethernet Phy está conectado a la interfaz EMAC. El PHY usa RTL8201, y el RTL8201 está conectado a la interfaz MII del DM365. El DM365 implementa la configuración y el control del registro RTL8201 a través de la interfaz MDIO. Las otras señales de apretón de manos están conectadas secuencialmente. El RTL8201 está configurado correctamente (configure la dirección PHY, etc.) tirando y tirando de la resistencia desplegable. El RTL8201 importa esta información de configuración al comienzo del encendido y realiza el trabajo correspondiente. Un cristal externo de 25 MHz está conectado a la interfaz del reloj del RTL8201 como la fuente del reloj para el RTL8201. El RTL8201 está conectado a un transformador de red para el aislamiento de la señal y está conectado a la red a través de RJ45.

2.3 Almacenamiento, USB, puerto serie, RTC, sistema de módulo de alarma proporciona una interfaz USB de 1 canal, admite el modo OTG y el modo de host, admite USB2.0 alta velocidad (480 MB/s), velocidad completa (12 MB/s), configure el Fifo. El controlador USB DM36 5 en chip y USB PHY completan su inicialización a través de la configuración relacionada, y los periféricos externos como el disco duro USB-SATA se pueden conectar al USB.

El sistema conecta externamente DDR2 SDRAM y NAND flash como memoria fuera de chip. El modo de arranque es el modo de arranque Nandflash configurando BTSEL [2: 0] a 000. La interfaz AEMIF de DM365 puede admitir Nandflash y Nor Flash. Debido a que NAND Flash tiene una gran capacidad de almacenamiento y bajo precio, este diseño usa NAND Flash.

DM365 proporciona una interfaz de control DDR2 dedicada, una línea de datos de 16 bits, una línea de dirección de 14 bits y señales de selección de 3 bloques, que pueden admitir 256 Mbyte de espacio de almacenamiento. El sistema utiliza el chip DDR2 SDRAM K4T1G164QQ.

DM365 tiene 2 interfaces UART, el sistema está conectado con dos puertos serie, un RS232, utilizado para la depuración y un periférico RS485 para la comunicación (lente PTZ, etc.). Y a través de GPIO para proporcionar una entrada de alarma de interruptor de 2 vías y la salida de alarma de interruptor de 2 vías, el diafragma realiza la entrada de alarma. Cuando se ingresa la señal de alarma, la luz se enciende y la salida es baja a DM365 GPIO, cuando no hay entrada de señal de alarma. Cuando la apertura se corta y la salida es alta a DM365 GPIO, el DM365 determina la presencia o ausencia de la señal de entrada de alarma al detectar el nivel GPIO. La salida de la alarma se realiza controlando la apertura y el cierre del relé. El sistema también extendió el RTC a través del IIC.

El sistema proporciona una entrada de reloj de 24 MHz al DM365 a través de un cristal externo y un reloj de módulo del PLL interno DM365.

2.4 Fuente de alimentación El sistema proporciona una interfaz de entrada de potencia de 5 V que proporciona +1.35 V, +1.8 V y +3.3 V de potencia a través del chip de conversión de potencia. Entre ellos, 1.35 V y 1.8 V son generados por TPS62040DGQ. El TPS62040DGQ es un chip DC-DC de alta eficiencia y baja ondulación de TI que regula el voltaje de salida a través de una resistencia. El voltaje de 3.3 V se implementa con el TPS5430, que tiene un voltaje de entrada máximo de 36 V y una corriente máxima de 3 A.

La secuencia de encendido para el sistema es: primero encender el núcleo (1.35V), luego encender el PLL y otros módulos (1.8V). Es decir, la fuente de alimentación de 3.3V se obtiene primero a través del TPS5430, entonces 1.35 V es generado por el TPS62040DGQ, y 1.8 V está conectado al EN de otro TPS62040DGQ a través de 1.35 V. Después de que se genera 1.8 V, la corriente se enciende la corriente. a través del interruptor. El resultado de 3.3 V, 3.3 V resultante, finalmente se carga en el DM365. El orden en el que se genera la potencia es opuesto a la secuencia de encendido.

3 Conclusión Para probar si el diseño cumple con los requisitos predeterminados, el rendimiento del sistema se ha probado a fondo. Se ha seleccionado una variedad de fuentes de entrada de video de alta definición para probar en diferentes entornos. Hay pruebas para la velocidad y la gravedad de la prueba. El blanco y negro del efecto de la imagen, así como el patrón de paso para probar el nivel de brillo.

Los resultados experimentales muestran que el sistema puede codificar en tiempo real, la imagen decodificada es clara y suave, no hay fenómeno de mosaico y animación, ni sobreexposición, falta de exposición al retrato, moldeo de color, exposición e inexactitud de equilibrio de blancos, etc., con colores brillantes y brillo claro. Superar las deficiencias en el sistema de monitoreo de definición estándar.

Esta solución de diseño es económica de usar, en línea con la intención original del diseño, y tiene amplias perspectivas de mercado en los campos del video, el sistema de monitoreo de alta definición y el monitoreo de vehículos.

Compartir:

Realizar consulta

Ms. carol Dong

Número de Teléfono:86-431-85543703

Fax:86-431---88634119

Móvil:+8613894866263

Email:sales@encoders.com.cn

Dirección:333Feiyue Donglu, Changchun City, Jilin Province. China, Changchun, Jilin

Sitio movil

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.